Les géants de la technologie forment un consortium pour normaliser les interfaces de puces

Les principales entreprises technologiques ont formé un consortium industriel pour développer un schéma d’interconnexion standard pour les puces, des puces plus petites interconnectées dans un seul boîtier pour fournir de multiples fonctions.

La complexité croissante des systèmes électroniques incite de plus en plus d’ingénieurs concepteurs à s’intéresser aux puces, des circuits intégrés qui contiennent des fonctions spécifiques sur des puces séparées qui sont ensuite interconnectées et conditionnées ensemble. Un obstacle à une plus grande acceptation a été le développement d’une méthode standard pour interconnecter ces matrices, afin d’améliorer la flexibilité de conception et l’approvisionnement.

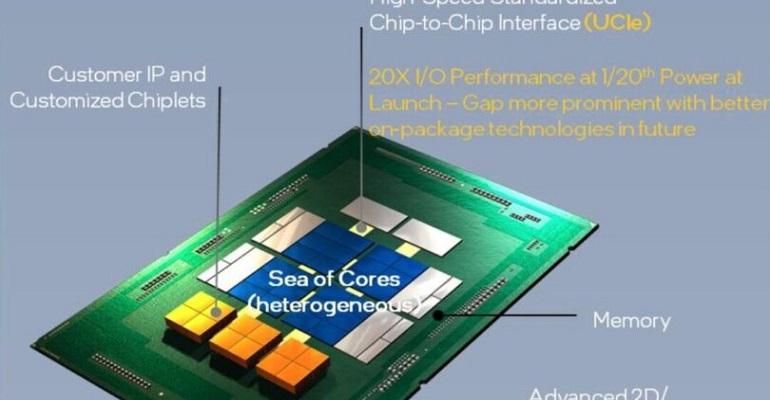

En réponse, un groupe d’entreprises technologiques de premier plan─Advanced Semiconductor Engineering, Inc., AMD, Arm, Google Cloud, Intel, Meta, Microsoft, Qualcomm, Samsung et Taiwan Semiconductor Manufacturing Company─a récemment formé un consortium industriel pour établir un die- to-die interconnect standard et promouvoir un écosystème de puces ouvertes, appelé le consortium UCIe. Les sociétés fondatrices ont ratifié la spécification UCIe 1.0, une norme industrielle ouverte développée pour établir une interconnexion au niveau du package.

La spécification couvre la couche physique d’E/S die-to-die, les protocoles die-to-die et la pile logicielle qui exploite les normes industrielles bien établies PCI Express® (PCIe®) et Compute Express Link™ (CXL™). La spécification sera disponible pour les membres de l’UCIe et téléchargeable sur le site Internet de l’UCIe.

Combiner plusieurs fonctions

Le concept de chiplets existe depuis plus d’une décennie, mais l’idée est peut-être née encore plus loin dans les années 1960, lorsque le scientifique Gordon Moore a suggéré dans un article technique, « Il peut s’avérer plus économique de construire de grands systèmes à partir de fonctions plus petites, qui sont emballées et interconnectées séparément. »

Dans un article technique sur la norme UCIe, l’auteur Le Dr Debendra Das Sharma, chercheur principal d’Intel et architecte en chef, membre promoteur des technologies et des normes d’E / S de l’UCIe, a noté que des pièces telles que les processeurs multicœurs avec un nombre de cœurs de l’ordre de mille pourraient bénéficier d’une configuration en tant que puce plus petite connectée dans un package , pour améliorer l’optimisation du rendement et favoriser la réutilisation des filières.

Les chiplets offrent aux ingénieurs plus de flexibilité dans la conception des produits et peuvent offrir un avantage en termes de délais de mise sur le marché. Les fonctions peuvent être implémentées dans différents nœuds de processus dans une configuration mixte en fonction des objectifs de conception. Les ingénieurs peuvent, par exemple, implémenter le processeur dans un nœud de processus plus avancé tandis que la mémoire, la logique et l’analogique sont implémentés dans des nœuds moins critiques.

Certaines entreprises intègrent déjà la technologie des puces dans leurs produits. Par exemple, Intel Les familles de FPGA et SoC Intel® Stratix® 10 GX, SX, TX et MX et les dispositifs FPGA Intel® Agilex™ utilisent la technologie de puces pour associer la puce logique FPGA aux tuiles d’E/S. DMLA Les processeurs de bureau haut de gamme Ryzen™ Threadripper™ 3970X et 3960X utilisent une conception de puces avec une matrice d’E/S centrale prise en charge par la technologie Infinity Fabric™ de la société.

Les deux sociétés utilisent différentes approches d’interconnexion dans leurs conceptions de packages Chiplet. Le protocole UCIe se normalisera sur une approche unique qui permettra aux entreprises de s’approvisionner mutuellement en silicium dans leurs produits, ce qui accélérera potentiellement les délais de mise sur le marché et réduira les coûts.

Protocole en couches

Étant donné que l’UCIe est une norme ouverte avec un modèle plug-and-play, les partisans de la norme pensent qu’elle sera facilement et largement adoptée. UCIe sera un protocole en couches. La couche physique est responsable de la signalisation électrique, de la synchronisation, de la formation des liens, de la bande latérale, etc. L’adaptateur Die-to-Die gère la gestion de l’état des liens et négocie les paramètres des chiplets. Le protocole fournit également un contrôle de redondance cyclique (CRC) et un mécanisme de nouvelle tentative au niveau de la liaison.

La norme définit deux types de conditionnement : un package 2D standard pour des performances économiques et un package avancé pour des performances économes en énergie. La norme prendra en charge deux grands modèles d’utilisation. Le premier est l’intégration au niveau du package pour offrir des performances économes en énergie et rentables. Le deuxième modèle d’utilisation consiste à fournir une connectivité hors package à l’aide de différents supports (optique, câble électrique, mmWave) en utilisant la propriété UCIe de Universal Chiplet Interconnect Express (UCIe) Retimers pour transporter les protocoles sous-jacents, afin d’atteindre les objectifs de puissance et de coût.

Selon l’UCIe, on s’attend à ce que la puce avec la conception de l’emballage standard interagisse avec toute autre conception de l’emballage standard. Dans le même ordre d’idées, une matrice avec la conception de boîtier avancée interagira avec toute autre matrice conçue pour le boîtier avancé, même dans la large gamme de pas de bosse de 25 u à 55 u.

OPCe Plus tard cette année, les sociétés membres commenceront à travailler sur la prochaine génération de technologie UCIe, y compris la définition du facteur de forme du chiplet, la gestion, la sécurité renforcée et d’autres protocoles essentiels.