Vous voulez en savoir plus sur PCB Fab, les émetteurs-récepteurs optiques et l’intégrité de l’alimentation ?

Apprenez des experts lors de la série de webinaires gratuits de cinq sessions DesignCon !

Cette semaine démarre une série de webinaires gratuits de cinq sessions mettant en vedette des ingénieurs expérimentés du programme de conférence de DesignCon, y compris des experts de Keysight Technologies, Intel, Picotest, NXP, Lamsim Enterprises et VSI Labs. Ces vétérans techniques partagent des idées et des connaissances pratiques pour concevoir la prochaine génération de technologies.

Vous pouvez vous inscrire à toutes les sessions ici. Si vous ne pouvez pas faire toutes les séances, ne vous inquiétez pas ! Tous seront consultables après chaque session. Voyons maintenant ce qui a été couvert au cours des premiers jours de la série de webinaires.

Sommaire

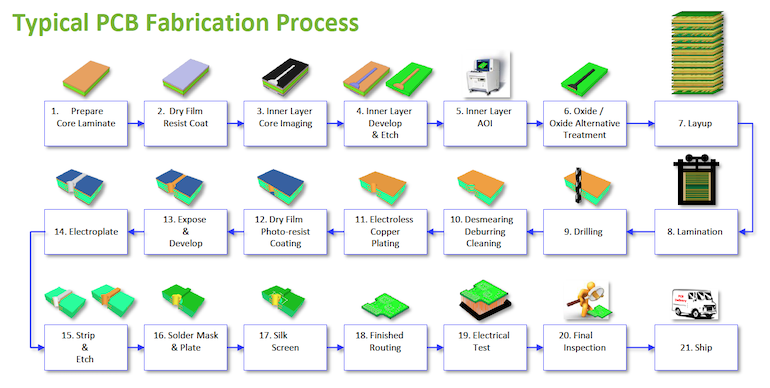

Fabrication de circuits imprimés pour les ingénieurs SI/PI

Lambert (Bert) Simonovich, président de Lamsim Enterprise, a fourni des directives importantes que les ingénieurs en intégrité du signal (SI) et en intégrité de l’alimentation (PI) doivent connaître lors de la première modélisation pour la fabrication de circuits imprimés. Il a parlé de la rugosité du conducteur, du retard de phase et de la perte d’insertion, y compris l’utilisation du modèle de rugosité Cannonball-Huray et comment l’appliquer dans plusieurs outils logiciels EDA. Simonovich a également expliqué comment extraire et appliquer les bonnes propriétés matérielles des fiches techniques des fabricants à utiliser pour la modélisation de canaux à grande vitesse. Il a conclu sa discussion en énumérant les avantages et les pièges de l’empilement des PCB sur l’intégrité de l’alimentation.

Pour référence, un dessin d’empilement de PCB est la première étape du processus de fabrication. Un empilement mal conçu et le manque de notes de fabrication détaillées peuvent entraîner une dégradation de l’intégrité du signal et de la puissance, de la fabricabilité et de la fiabilité du produit fini. Souvent, les ingénieurs SI/PI font des hypothèses de conception erronées, ce qui conduit à des résultats de modélisation et de simulation inexacts. Pour cette raison, ils doivent comprendre les nuances de conception et de fabrication des PCB pour éviter les pièges dans la réalisation de modèles utiles pour la première fois.

Le processus typique de fabrication de PCB.

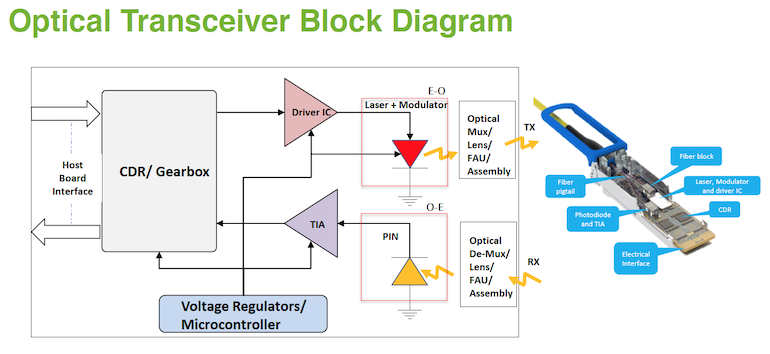

Conception d’émetteur-récepteur optique

Les centres de données à grande échelle (HSDC) nécessitent généralement des millions d’émetteurs-récepteurs optiques, créant une énorme demande pour les produits 400G/800G. La croissance exponentielle de la communication de données induite par HSDC en raison de l’informatique en nuage, du stockage en nuage, de la réalité augmentée (AR), de la réalité virtuelle (VR), de la vidéo à la demande (VoD), de la 5G, de l’Internet des objets (IoT) et de la conduite autonome sont les dictant des facteurs pour une bande passante beaucoup plus élevée et une consommation d’énergie plus faible.

La conception d’émetteurs-récepteurs optiques est un processus complexe car elle nécessite que plusieurs disciplines telles que l’électricité, la mécanique, l’optique et le micrologiciel se réunissent précisément pour fournir les performances électro-optiques requises. Le concepteur fait face à des défis importants dans la conception d’émetteurs-récepteurs 800 Gbit/s en raison de leur facteur de forme, de leur vitesse élevée, de leur consommation d’énergie élevée et de leur densité de canaux. Maintenant que les émetteurs-récepteurs 800 Gbit/s en sont à leur première phase d’échantillonnage, l’industrie optique a déjà entamé la discussion sur la prochaine génération d’émetteurs-récepteurs optiques offrant une bande passante de 1,6 Tbit/s et 3,2 Tbit/s.

La conception de ces nouvelles générations d’émetteurs-récepteurs nécessitera un niveau d’intégration beaucoup plus élevé et de nombreuses avancées technologiques et d’emballage. Pour se préparer à cette technologie, les ingénieurs doivent comprendre les bases des émetteurs-récepteurs optiques et discuter de la conception des émetteurs-récepteurs 400 Gbit/s, 800 Gbit/s et de nouvelle génération.

Deux experts d’Intel ont fourni une bonne introduction à ces fondamentaux. Sunil Priyadarshi, directeur d’Intel, et Sanjeev Gupta, ingénieur principal et directeur R&D d’Intel, ont commencé leur discussion par un examen des bases des émetteurs-récepteurs optiques. Une grande partie de leur discussion s’est ensuite concentrée sur les considérations de conception pour les émetteurs-récepteurs 400/800 Gbps, y compris les avantages des optiques co-packagées pour obtenir une réduction de puissance améliorée au niveau du système par rapport à la plaque avant enfichable et avec des SerDes à puissance optimisée pour la puce intégrée canal -vers-OE

Un schéma fonctionnel d’un émetteur-récepteur optique.

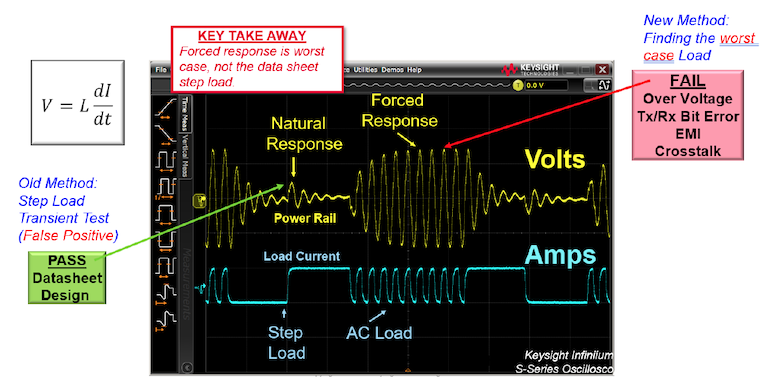

Conseils d’impédance pour améliorer l’intégrité de l’alimentation

L’intégrité de la puissance consiste à fournir la puissance appropriée pour maintenir l’intégrité du signal (SI) des charges dynamiques, le tout avec des marges de conception de fourniture de puissance qui permettent des performances de produit fiables. Le principal défi pour l’ingénieur PI est que la charge dynamique peut fonctionner de CC à GHz, ce qui entraîne des bandes passantes extrêmes de fourniture d’énergie et un potentiel d’EMI. L’impédance cible par rapport à la fréquence est un excellent outil pour concevoir une alimentation électrique sur toute la bande passante de la charge dynamique, mais les concepteurs ne parviennent souvent pas à tirer pleinement parti de ses avantages.

Heidi Barnes, ingénieur d’applications SI et PI chez Keysight Technologies, et Steve Sandler, fondateur et président de Picotest.com, ont partagé des informations techniques utiles sur la façon de rétro-concevoir l’impédance cible pour générer des exigences pour l’inductance active du VRM et le boîtier/matrice de charge. capacitance. Ils ont encouragé les ingénieurs à suivre des techniques de conception à impédance plate pour améliorer les marges de conception par rapport aux tolérances des composants et éviter le désastre d’une onde de tension parasite arrivant à la charge. Enfin, ils ont exploré des simulations avancées dans le domaine temporel de l’écosystème PI avec des modèles de PCB EM pour comprendre le rapport de rejet de l’alimentation (PSRR) et les sources potentielles d’EMI conduites.

La fourniture d’énergie pour les charges numériques est AC, pas DC.

Les éléments suivants sont encore à venir cette semaine :

- Jeudi 15 avril 2021, 13h00 HAE : « Contrôler les ondes : une perspective basée sur le terrain sur la conception de circuits imprimés à grande vitesse », par Daniel Beeker, ingénieur principal principal, NXP

- Vendredi 16 avril 2021, 13 h 00 HAE : « OEM Roundup 2021 : le nouvel ADAS », par Danny Kim, directeur des services consultatifs, VSI Labs

En plus des sessions de webinaires gratuites, les participants auront également la possibilité de profiter d’une session de réseautage à la fin de la semaine avec des conférenciers sélectionnés de la conférence de DesignCon, où ils pourront rencontrer d’autres participants, organiser des réunions en tête-à-tête et faire connaissance avec des pairs de l’industrie.

Ne vous inquiétez pas si vous avez manqué quelques séances. Ils seront disponibles à la demande pour être visionnés. De plus, les participants au webinaire Spring Break peuvent également s’attendre à recevoir un code de réduction pour assister à la conférence annuelle en personne de DesignCon qui aura lieu au San Jose McEnery Convention Center, du 16 au 18 août 2021.

John Blyler est rédacteur en chef de Design News, couvrant les domaines de l’électronique et de la fabrication de pointe. Titulaire d’un BS en ingénierie physique et d’une maîtrise en génie électrique, il a des années d’expérience en systèmes matériel-logiciel-réseau en tant qu’éditeur et ingénieur dans les secteurs de la fabrication de pointe, de l’IoT et des semi-conducteurs. John a co-écrit des livres sur l’ingénierie système et l’électronique pour IEEE, Wiley et Elsevier.